1. 写事务信号

- dfi_wrdata:写入数据。

- dfi_wrdata_mask:用于掩码操作的数据掩码。

- dfi_wrdata_en:写数据使能信号,它指示什么时候数据传输开始。

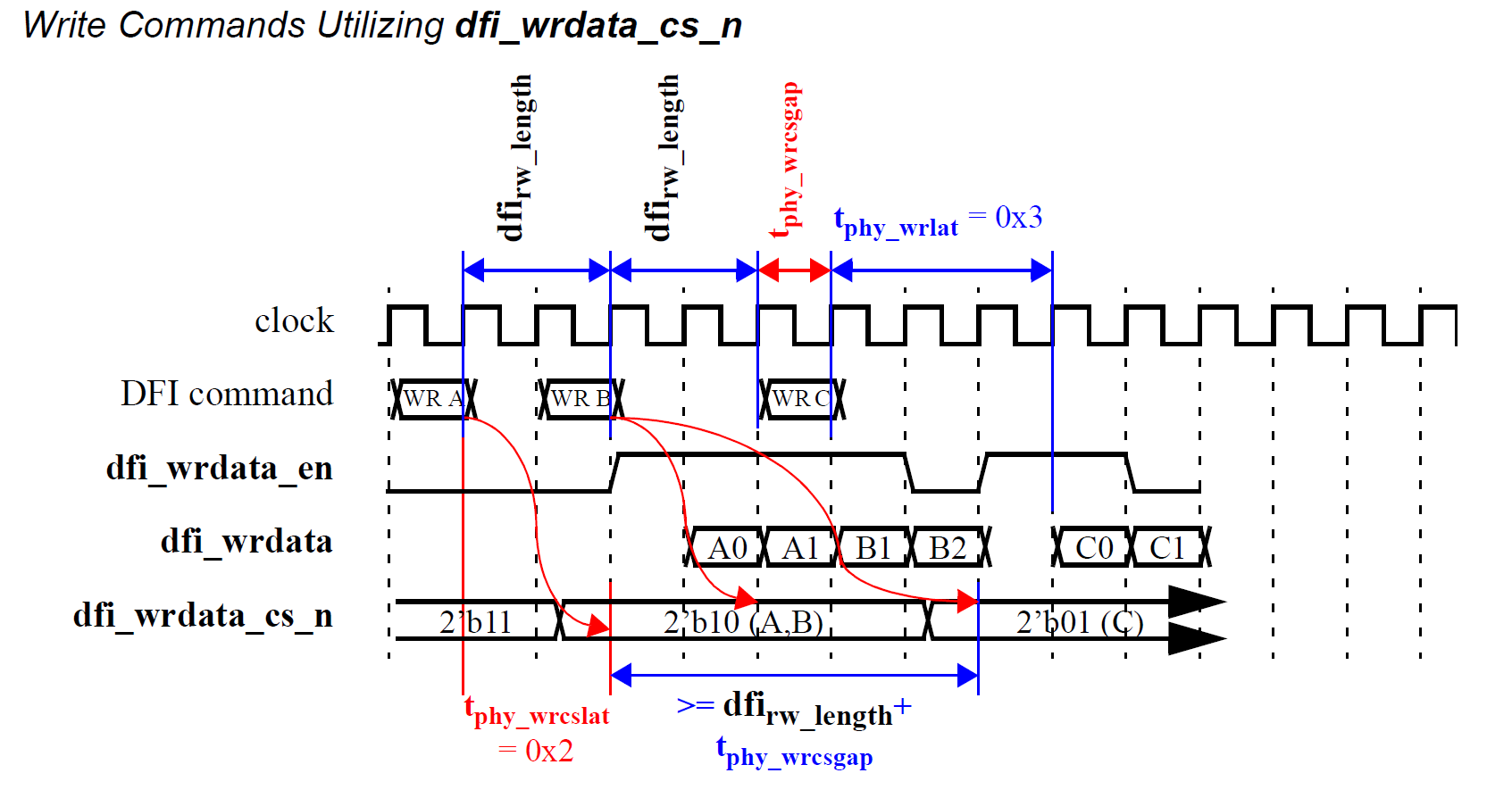

- dfi_wrdata_cs_n(可选):写数据片选信号,它可以用于选择数据路径的目标(即选择哪个物理数据片)。

相关时序参数:

tphy_wrlat:从写命令开始到dfi_wrdata_en信号有效之间的周期数(这个延迟时间通常与 DRAM 时序一致)。tphy_wrdata:从dfi_wrdata_en激活到实际数据传输的时间。phycrc_mode和phydbi_mode:这两个可编程参数控制是否启用 CRC 和 DBI 功能。

2. dfi_wrdata_en 信号的作用

dfi_wrdata_en 信号需要与 DRAM 总线上的数据传输数量相匹配。这个信号可以在多个写命令中持续有效,以表示传输多个数据周期。

- 如果启用了 写数据片选(dfi_wrdata_cs_n),该信号将选择目标数据路径的片选值。

3. 写事务的时序和步骤

3.1 步骤 1:发布写命令

- 首先,写命令会通过 DFI 接口发布给 PHY。这个命令告诉 DRAM 进行写操作。

3.2 步骤 2:tphy_wrlat 延迟

- 在写命令发布后,

tphy_wrlat个周期会延迟。这个延迟代表从写命令到dfi_wrdata_en激活之间的周期数。 - 如果启用了写数据片选功能,可能还会有

tphy_wrcslat延迟,用来定义写数据片选信号的时序。

3.3 步骤 3:片选时序(如果启用)

- 如果启用了片选功能,内存控制器(MC)将控制

dfi_wrdata_cs_n信号,并确保它在规定的时间内保持激活状态,直到数据传输完成。 tphy_wrcslat是 PHY 定义的参数,控制写命令和片选信号之间的对齐方式;tphy_wrcsgap控制两个连续命令之间的间隙。

3.4 步骤 4 和 5:激活 dfi_wrdata_en 信号

- 对于非连续的写命令,

dfi_wrdata_en信号在满足tphy_wrlat延迟后激活,并保持足够长的时间以完成数据传输。 - 对于连续写命令,

dfi_wrdata_en信号将在tphy_wrlat延迟后持续激活整个数据流的长度。

3.5 步骤 6:tphy_wrdata 周期

- 在

dfi_wrdata_en信号有效后,系统会等待tphy_wrdata个周期,这是从dfi_wrdata_en到写数据实际传输开始的时间。

3.6 步骤 7:传输写数据和掩码

- 在此时,

dfi_wrdata和dfi_wrdata_mask信号会被用来传输实际的写数据和数据掩码(如果启用了掩码功能)。 - 如果启用了 CRC 功能,内存控制器还会将 CRC 数据通过

dfi_wrdata传输到 PHY。 - 如果启用了 DBI(数据总线反转),

dfi_wrdata_mask会传输数据反转信息,而不是掩码。

3.7 步骤 8:dfi_wrdata_en 信号取消

- 当所有数据传输完成后,

dfi_wrdata_en信号会在数据传输结束前的tphy_wrdata周期取消激活。

3.8 步骤 9:进入空闲状态

- 一旦所有数据传输完成,

tphy_wrdata_delay个周期后,DFI 总线将进入空闲状态。

4. 写事务与其他功能(CRC 和 DBI)

- 如果启用了 CRC 功能,内存控制器将延长

dfi_wrdata_en信号,以适应扩展的 DRAM burst 长度,可能会出现奇数个周期的写入。 - 如果启用了 DBI 功能,

dfi_wrdata_mask信号将用于传输写数据反转信息,而不是用于掩码。

5. 时序的影响

- 在 连续写命令 的情况下,

dfi_wrdata_en信号会一直有效,直到整个数据流完成,而在 非连续写命令 中,dfi_wrdata_en信号仅会在需要的周期内激活。 tphy_wrlat、tphy_wrdata和tphy_wrdata_delay参数需要精确设置,以确保数据在正确的时间传输到 DRAM。

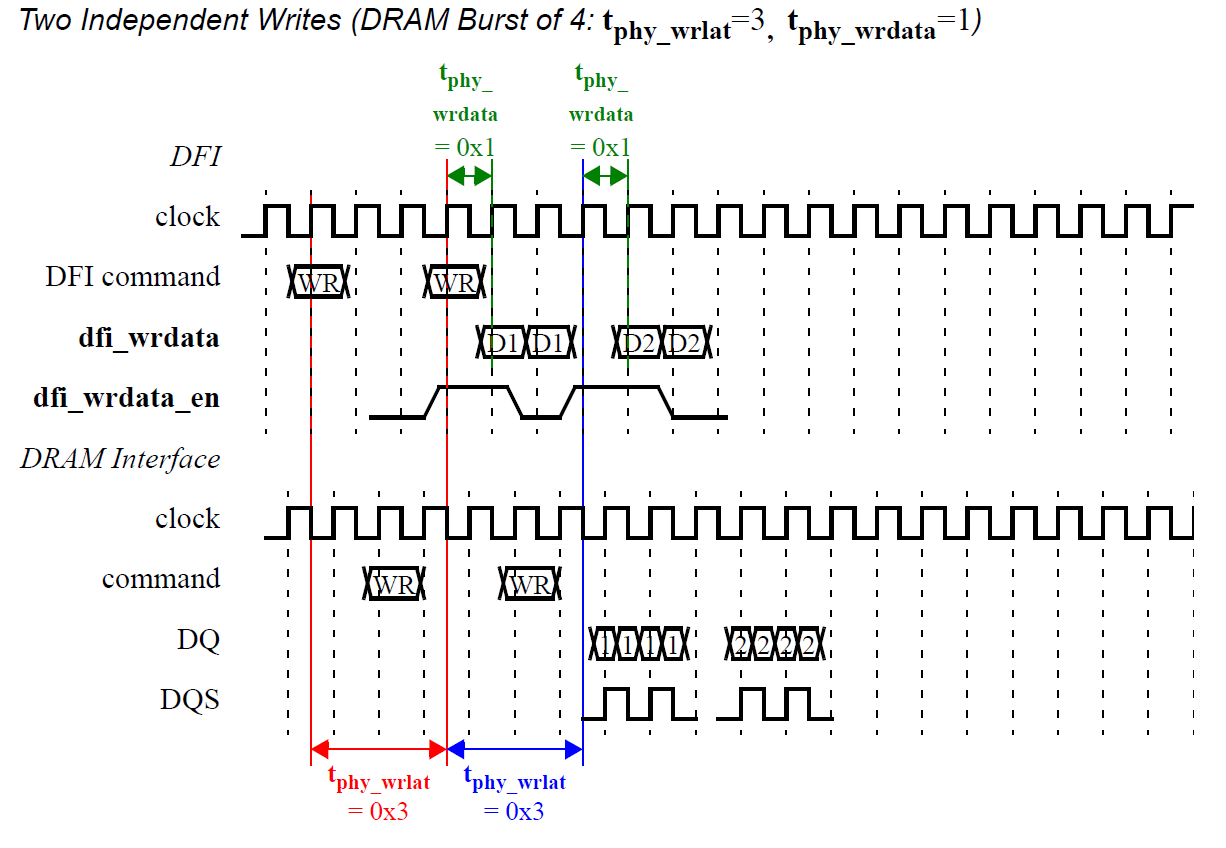

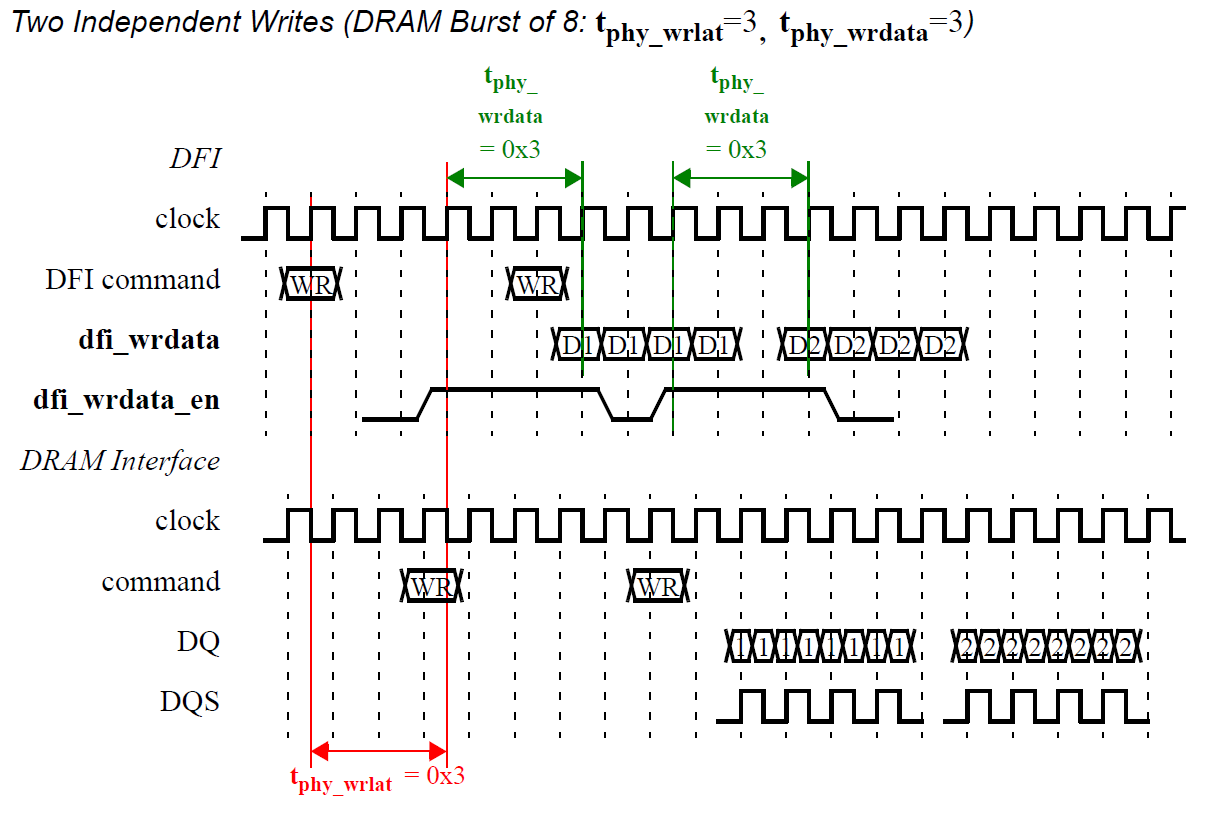

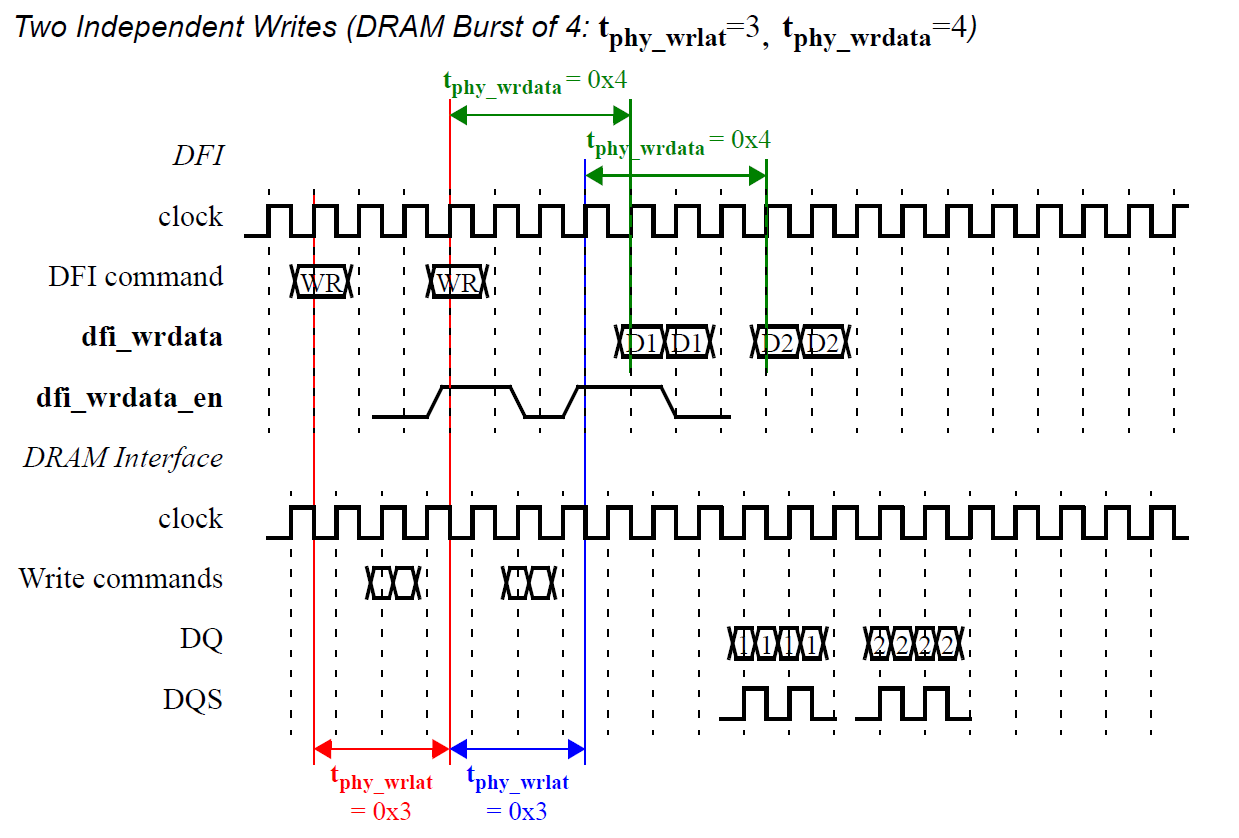

6. 写事务的时序图

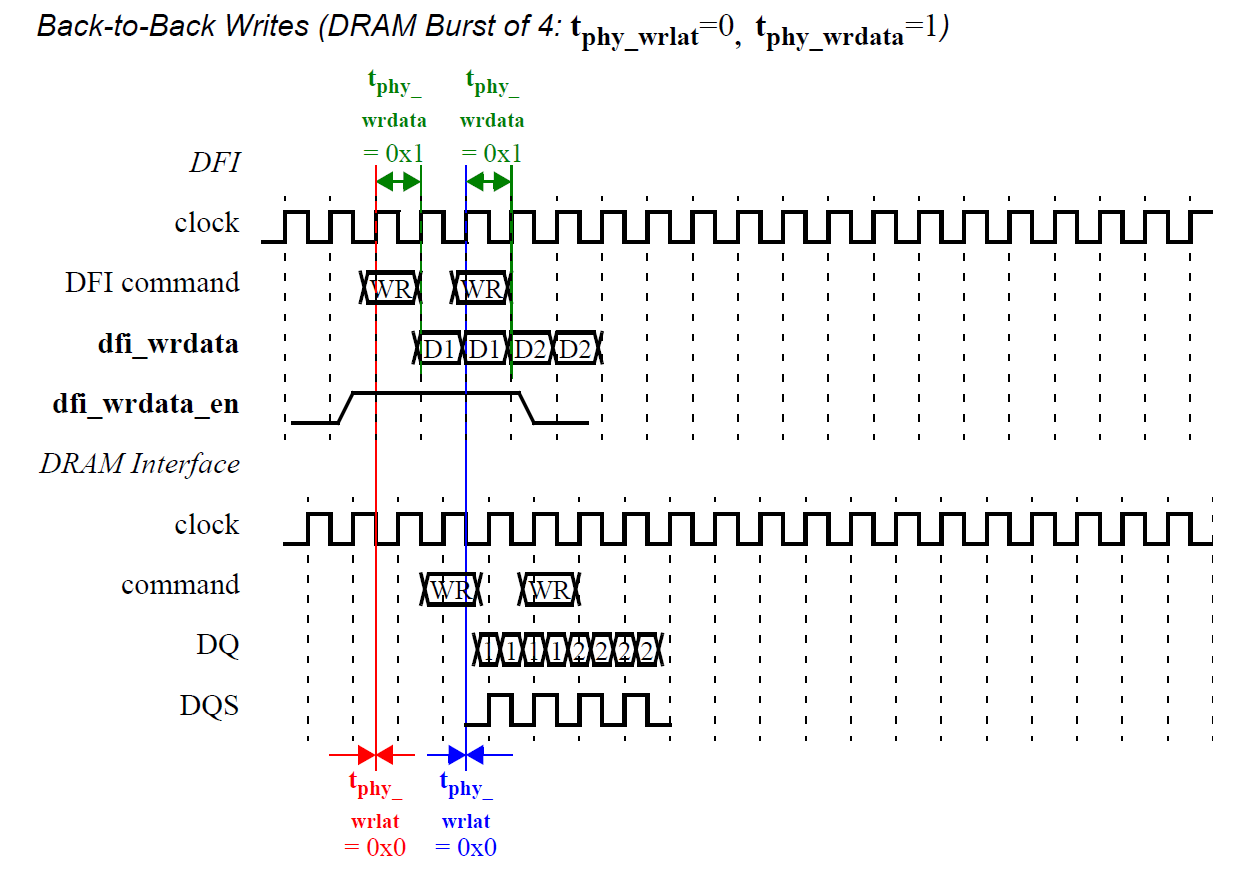

章节最后提到了一些图表,展示了不同写事务情况下的系统行为。例如

- 图 8 显示了一个具有

tphy_wrlat为0和tphy_wrdata为1的系统,展示了如何连续发送两个写命令。

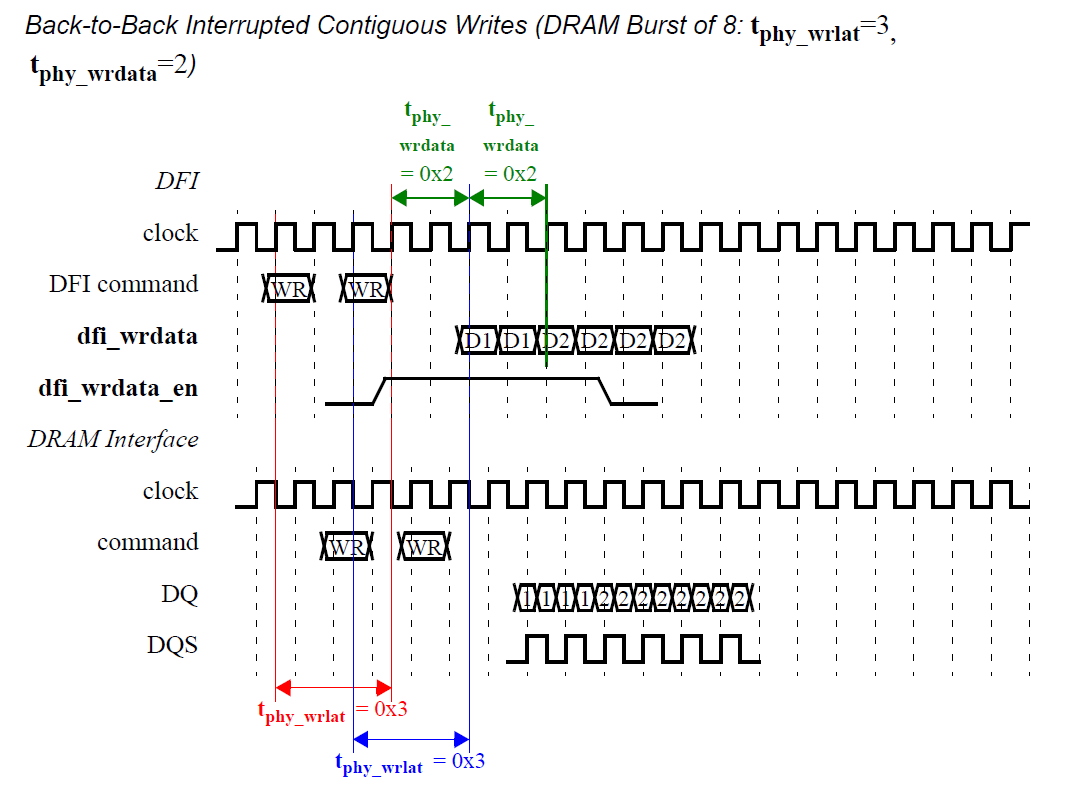

- 图 9 显示了一个中断的写命令。对于每个写事务,

dfi_wrdata_en信号应该保持激活 4 个周期。然而,由于第一个写事务被中断,dfi_wrdata_en信号只会在第一个事务的部分周期内保持激活,并在第二个事务的整个周期内保持激活。dfi_wrdata_en信号在写命令之间不会取消激活,且dfi_wrdata数据流将在第一个命令的部分周期和第二个命令的整个周期内连续发送。

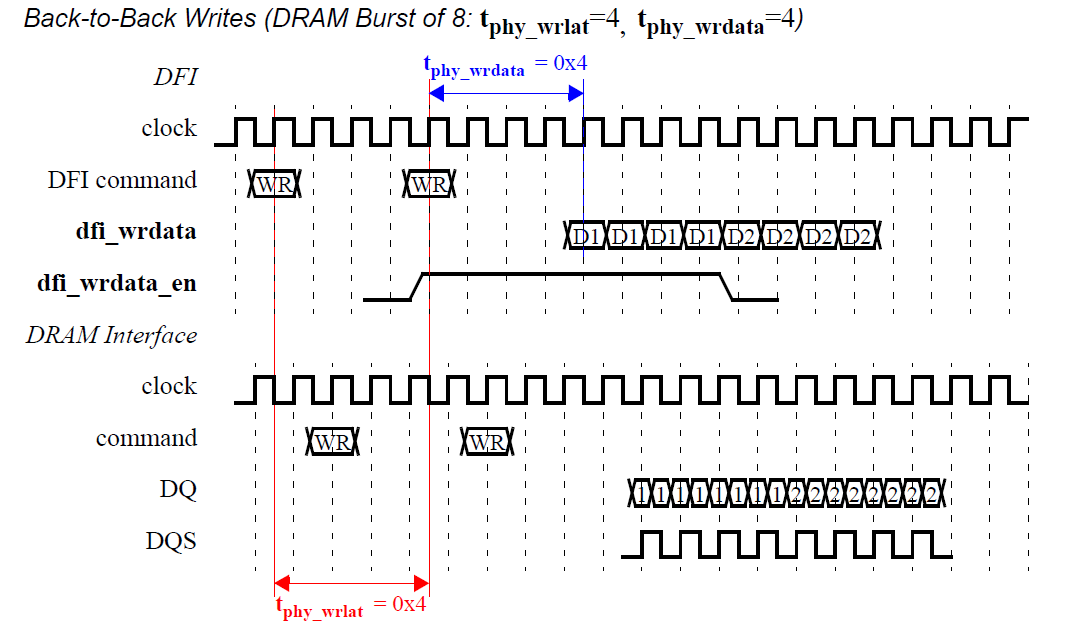

- 图 10 显示了连续的 8 位突发写操作。对于这些写事务,

dfi_wrdata_en信号必须在每个写事务中保持激活 4 个周期。

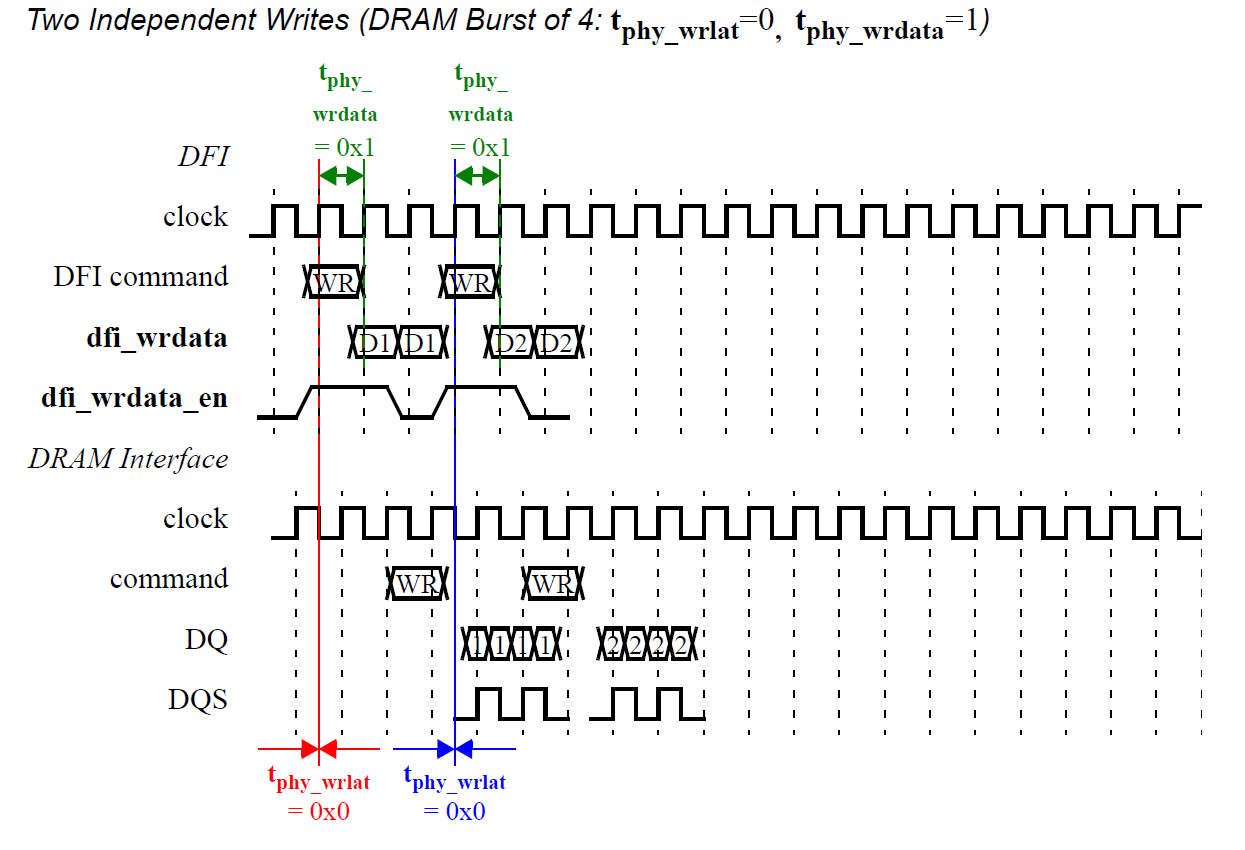

- 图 11、图 12、图 13 和图 14 也展示了两个完整的写命令,具有不同的

tphy_wrlat和tphy_wrdata时序参数,并且适用于不同的 DRAM 类型。在每个写事务中,dfi_wrdata_en信号会保持激活 2 个周期。tphy_wrlat时序和写命令之间的时序关系导致dfi_wrdata_en信号在命令之间被取消激活。因此,dfi_wrdata数据流是非连续的。

- 图 15,“使用

dfi_wrdata_cs_n的写命令” 显示了三个写命令,其中第二个和第三个命令之间有一个间隙。

4.4.2 DBI - 写操作

DBI (Data Bus Inversion) 是一个可选的 DFI 功能,用于写数据传输中。其主要目的是通过反转数据来提高信号的质量,减少总线上的电气干扰,或者是优化功耗。这个功能特别有助于降低数据总线上的直流成分,从而减少功耗。

关键概念:

- phydbi_mode 参数:

phydbi_mode是一个参数,定义了如何处理 DBI 数据。- 这个参数仅在支持 DBI 功能的 DFI 系统中才需要。

- 如果你需要更详细的

phydbi_mode参数信息,可以参考协议中第 33 页的表 7(“写数据时序参数”)。

- MC(内存控制器)生成写 DBI 数据:

- 当内存控制器(MC)生成写数据时,它会根据需要对数据进行反转。

- 反转后的写数据通过 DFI 总线上的

dfi_wrdata_mask_pN信号传输。 - 在 DBI 模式下,PHY(物理层)只需要将写 DBI 数据从 MC 传输到 DRAM(动态随机存储器)。

- 写数据传输与 DBI 数据传输同步:

- 在写数据传输的同时,DBI 数据也会通过

dfi_wrdata_mask信号传输。dfi_wrdata_mask信号与对应的dfi_wrdata数据总线是同步传输的。 - 这种传输确保了 DBI 数据与正常写数据在时间上对齐。

- 在写数据传输的同时,DBI 数据也会通过

- 频率比系统的处理:

- 对于具有不同频率比的系统(例如,内存控制器的频率与 DRAM 的频率不同),

dfi_wrdata_mask信号会被延长,并为每个时钟相位定义一个信号。

- 对于具有不同频率比的系统(例如,内存控制器的频率与 DRAM 的频率不同),

- DBI 与 CRC 共存时的注意事项:

- 如果系统同时启用了 DBI 和 CRC(循环冗余检查),需要特别注意它们的执行顺序。不同的执行顺序会影响数据的正确传输和系统的整体操作。

4.4.3 循环冗余检查(CRC)

CRC (Cyclic Redundancy Check) 是另一种可选的 DFI 功能,用于写数据传输中。在写数据突发传输中,CRC 用于检测数据的完整性,确保数据在传输过程中没有错误。

关键概念

CRC 数据的作用:

- CRC 的作用是对写数据进行错误检测,它会将一个标准的 8 单元周期(UI)的写数据突发延长到 10 UI(原来是 8 UI)。

- 通过这样做,CRC 增加了额外的周期来容纳 CRC 校验数据,从而使数据传输更加可靠。

MC 和 PHY 的 CRC 数据生成:

- 在支持 CRC 的系统中,MC 或 PHY 可以生成 CRC 数据。具体由谁生成 CRC 数据取决于系统的设置。

- 如果 PHY 没有生成 CRC 数据,则必须由 MC 生成 CRC 数据。

phycrc_mode 参数:

phycrc_mode是一个可编程参数,定义了是 MC 生成 CRC 数据,还是 PHY 生成 CRC 数据。phycrc_mode == 0:由 MC 生成 CRC 数据。phycrc_mode == 1:由 PHY 生成 CRC 数据。

phycrc_mode参数仅在系统支持 CRC 的情况下使用。

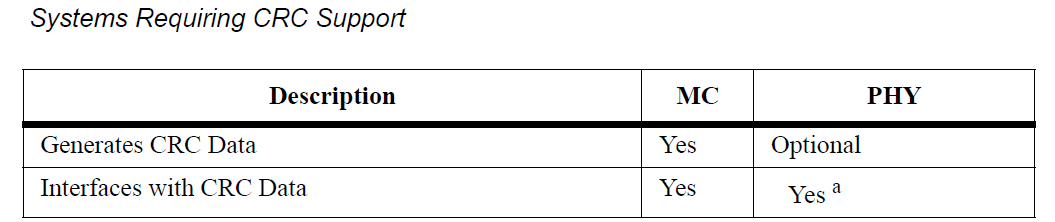

CRC 支持的系统要求:

- 在支持 CRC 的系统中,必须能够满足特定的条件,才能正确实现 CRC 功能。详细的系统要求在协议中的 表 23(“需要 CRC 支持的系统”)中列出了。

- a -> 如果 PHY 不生成 CRC 数据,则此项是必需的。

- 无论是哪个设备生成 CRC,MC 都会使能 ODT 信号,以确保它适用于所有发送的数据和 CRC 数据字。

4.4.3.1 MC CRC Support (phycrc_mode ==0)

1. CRC的生成和使用

- DFI信号:

dfi_wrdata_en是指示数据传输的信号,包括CRC数据。当phycrc_mode为0时,MC必须在传输数据时激活此信号。这意味着,不论是正常数据还是CRC数据,都要在传输时使能这个信号。

2. 命令和数据传输

- Extended Burst:MC需要适当地间隔命令,以支持带有CRC的扩展数据突发。CRC的存在可能使得数据突发的长度变化,因此MC需要合理安排命令发出间隔以兼容这些变化。

3. ODT信号的处理

- dfi_odt(Data Termination) :用于DRAM的写入和读取操作。MC应根据包含CRC数据的DRAM突发长度生成此信号。在启用CRC的情况下,MC可能需要扩展ODT的时间,以确保正确的数据传输和校验。

4. 错误信息的捕获

- 错误信息处理:MC还需要接收来自PHY的错误信息,例如CRC写入数据错误。这些错误信息通过信号

dfi_alert_n_aN传输。MC必须支持这个输入信号。如果PHY不生成这个信号,MC的输入应保持在一个未被激活的状态。

5. 不规则突发支持

- 奇数周期的支持:在使用CRC的情况下,

dfi_wrdata_en信号可以在每个突发周期的奇数次被激活。这意味着PHY必须支持这种特殊的突发时序。

6. CRC数据的整合

- 数据传输中的CRC整合:DFI协议要求在使用CRC时,CRC数据必须包含在写数据的突发中。然而DFI并未规定CRC数据的具体位置。因此,MC在设计时可以灵活安排CRC数据的位置,但必须确保它们与数据一起传输。

7. ODT信号的时序

- ODT信号的时序一致性:无论在MC CRC支持模式还是PHY CRC支持模式下,

dfi_odt信号的激活和去激活时序是相同的。文中提到的时序只是众多可能解决方案中的一种。

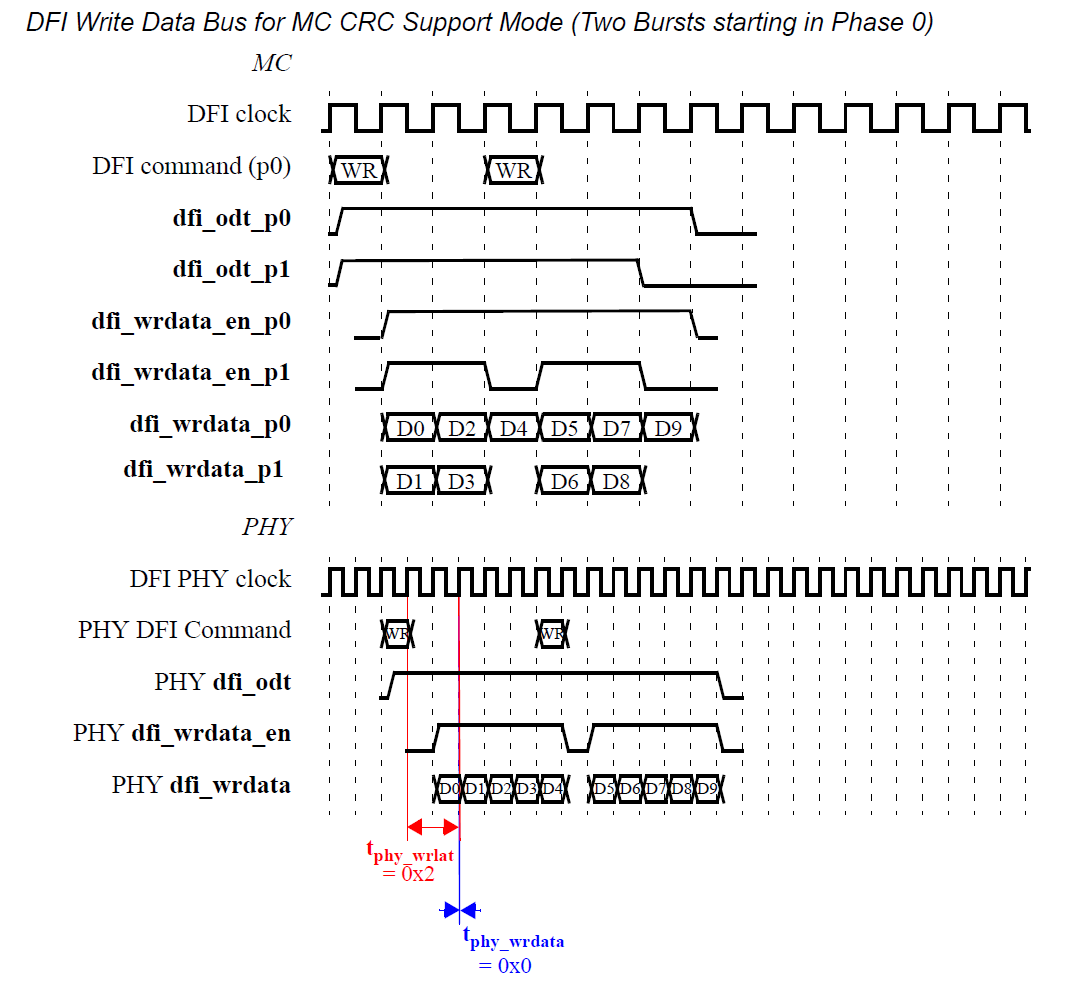

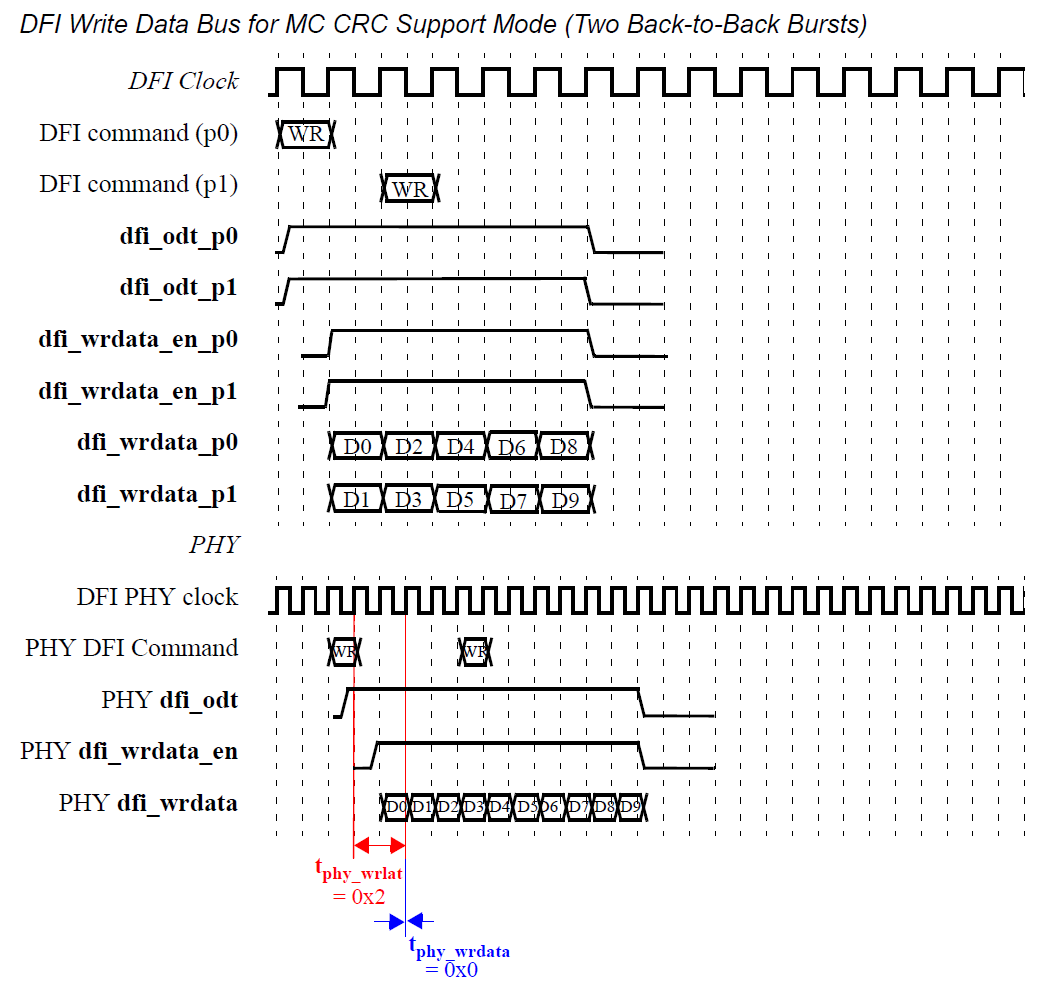

8. 示例图和对比

- 章节提到的图(如Figure 16和Figure 18等)显示了在不同模式下DFI写数据总线的时序图。这些图为设计人员提供了在实施时可能采用的时序模式的可视化示例。

- Fig 16

- Fig 17

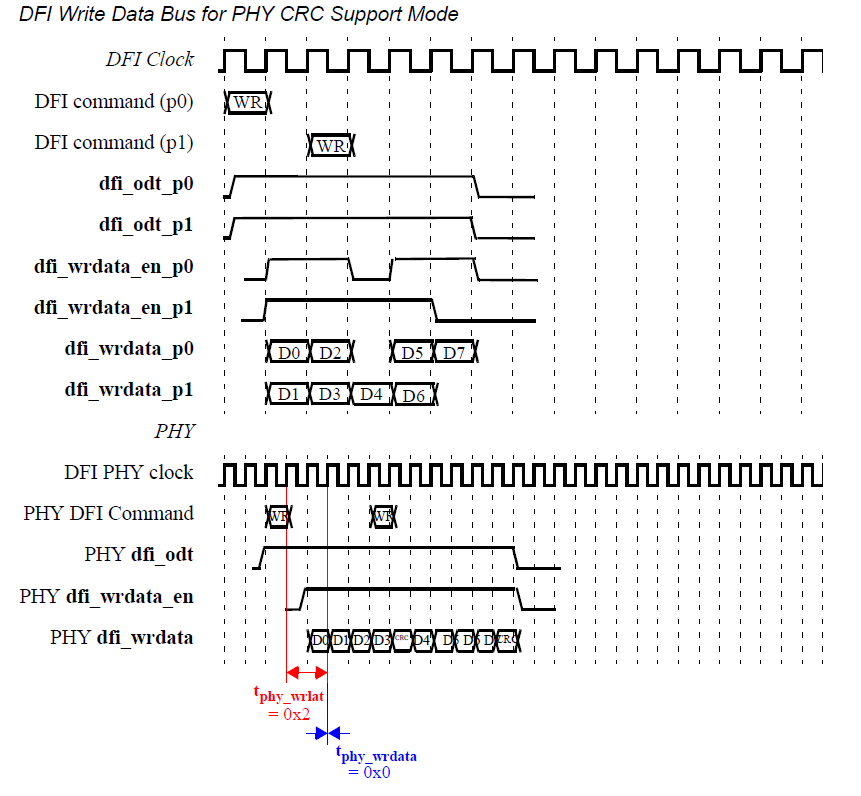

4.4.3.2 PHY CRC Support (phycrc_mode == 1)

这段内容解释了当 PHY 生成 CRC 数据 时(即 phycrc_mode == 1),内存控制器(MC)和 PHY 之间的交互规则。与 MC 生成 CRC 数据的情况(phycrc_mode == 0)不同,在 phycrc_mode == 1 时,MC 和 PHY 之间有一些关键的时序和控制要求。

1. MC 禁用 CRC 生成逻辑

- 当

phycrc_mode == 1时,MC 不再负责 CRC 数据的生成。因此,MC 必须禁用其 CRC 生成逻辑。这样,CRC 数据不会通过 DFI 总线由 MC 传输。MC 只需要传输数据,而不包括 CRC 数据。

2. MC 仅对写数据断言 dfi_wrdata_en 信号,不对 CRC 数据断言

- 在

phycrc_mode == 1时,MC 只需要对写数据断言dfi_wrdata_en信号,而不需要对 CRC 数据进行断言。这意味着dfi_wrdata_en信号仅覆盖实际的写数据,不包括 CRC 数据,因为 CRC 数据由 PHY 负责生成和传输。

3. MC 需要处理带 CRC 的扩展突发

- 即使在

phycrc_mode == 1情况下,MC 仍然需要处理带有 CRC 的扩展突发。由于 CRC 增加了突发的时序要求,MC 需要管理命令间的间隔,以适应这个额外的周期。MC 需要保证时序正确,以便能够传输带 CRC 的扩展突发数据。

4. MC 生成 dfi_odt 信号

- 即使 CRC 数据是由 PHY 生成的,MC 仍然需要基于 DRAM 突发长度(包括 CRC 数据)来生成

dfi_odt信号。当启用 CRC 时,MC 可能需要扩展 ODT(On-Die Termination)时间,以确保包括 CRC 数据在内的所有数据都能完整传输。dfi_odt信号的断言和去断言与phycrc_mode == 0时相同。

5. MC 必须接收并捕获来自 PHY 的错误信息

- 与

phycrc_mode == 0相似,MC 仍然需要接收来自 PHY 的错误信息,这些错误会通过dfi_alert_n_aN信号传输给 MC。如果 PHY 没有生成dfi_alert_n_aN输出,MC 必须将此输入信号保持在去断言状态。

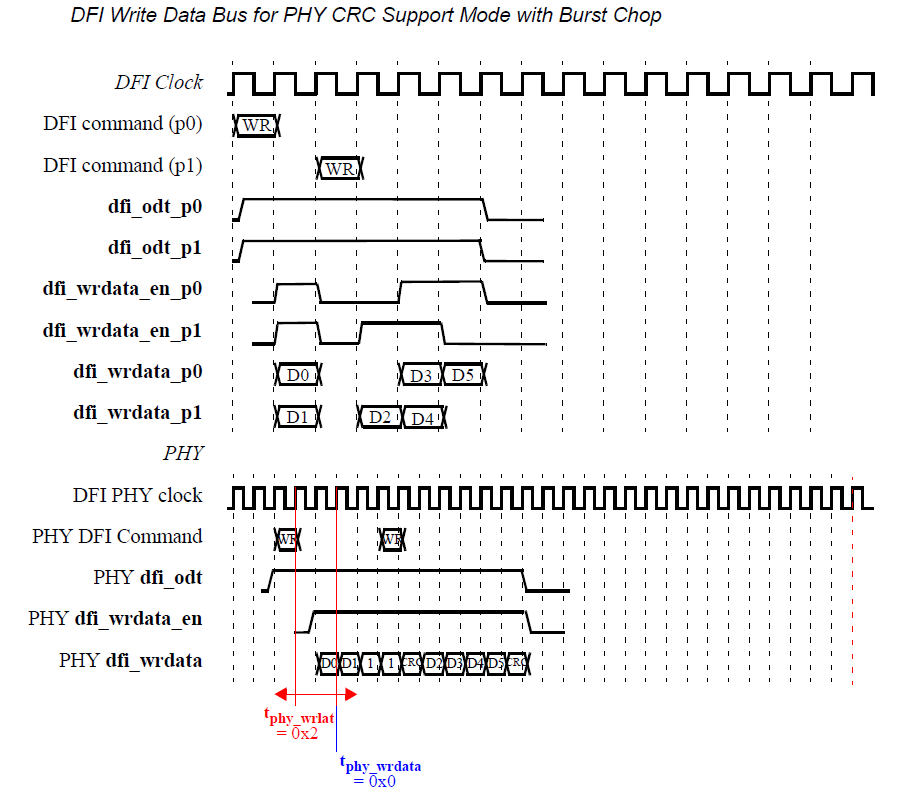

4.4.3.3 Burst Chop 4 with PHY CRC Support (phycrc_mode == 1)

Burst Chop4(BC4) 是一种特殊模式,在这种模式下,内存突发会被扩展以适应 CRC 数据的传输,类似于一个 8 单位时间(UI)的突发延长为 10 UI。这一节描述了当 PHY 生成 CRC 数据时,MC 和 PHY 之间如何处理这种扩展突发。

1. BC4 模式下,MC 不会调整 dfi_wrdata_en_pN 信号

- 在 BC4 模式下,内存的突发周期会延长,以适应 CRC 数据的传输。然而,MC 不需要调整

dfi_wrdata_en_pN信号,即 MC 在突发时不会专门考虑 CRC 数据的传输。MC 只需要按照常规的数据传输规则来传输写数据。

2. PHY 使用 dfi_wrdata_en_pN 信号的宽度来判断突发类型

- 在支持动态突发长度和 BC4 的系统中,PHY 可以使用

dfi_wrdata_en_pN信号的宽度来判断是普通的 8 单位时间(UI)突发,还是 BC4 模式下的扩展突发。这种机制使得 PHY 可以根据突发的长度来决定何时生成 CRC 数据,并且根据数据的宽度来安排 CRC 的传输。

3. CRC 数据在突发的末尾传输

- 在 BC4 模式下,CRC 数据通常位于突发的末尾。图 18 和图 19 展示了这种情况,其中 CRC 数据位于突发的最后一个数据字的位置。具体来说,CRC 数据字的位置取决于 DRAM 的要求。

4. dfi_odt 信号的时序要求

- 在

phycrc_mode == 1下,dfi_odt 信号的时序要求与phycrc_mode == 0相同。也就是说,dfi_odt 信号的断言和去断言操作涵盖了写数据和 CRC 数据的传输。在这种模式下,dfi_odt信号会被扩展,以确保 CRC 数据的完整传输。

5. BC4 和 8 单位时间(UI)突发中的 CRC 数据传输

- 对于 BC4 和普通的 8 UI 突发,CRC 数据在突发的最后 2 个时钟周期(UI9 和 UI10)传输。因此,CRC 数据总是位于突发的末尾,无论是 BC4 模式还是 8 UI 模式,CRC 数据都会被附加在写数据之后传输。

Fig 18

Fig 19

本文链接: https://talent-tudou.github.io/2024/12/28/DFI/DFI Spec-Write Transactions/

版权声明: 本作品采用 CC BY-NC-SA 4.0 进行许可。转载请注明出处!